Opella-XD Debug Probe

Ashling’s Opella-XD is a universal, high-speed debug probe for embedded development supporting a broad range of MCUs, SoCs and Soft (FPGA) based designs for all popular target architectures including Arm, MIPS, RISC-V and Synopsys ARC.

Opella-XD Debug Probe

Opella-XD Features:

- Up to 3MB/s download speeds making it suitable for large, complex, software-intensive projects.

- Fast, trouble-free “plug-and-play” installation using USB 2.0 High-Speed Interface (480Mb/s).

- Powered by USB interface – no external power-supply required.

- JTAG (IEEE 1149.1), cJTAG (IEEE 1149.7) and Arm CoreSight Serial Wire Debug (SWD) standards supported.

- Fine-grained adjustment of cJTAG/JTAG/SWD clock frequency from 1kHz to 100MHz.

- Auto-conditioning support provides maximum possible download speed to target with fastest cJTAG/JTAG/SWD clock frequencies.

- Hot-plug support – allows connection to a running target without resetting or halting.

- Supports target operating voltages from 0.9V to 3.6V– probe detects and automatically configures for the appropriate target voltage.

- Configurable Target-Reset and Test-Port-Reset, under full user control.

- Built-in diagnostics and LEDs instantly show status of Target, Debug Probe and USB link.

- Low-level JTAG command-line console and APIs for device bring-up etc.

- Display/read/write of target system memory and peripheral registers.

- Fast in-target Flash and FPGA programming.

- Support for all on-chip hardware breakpoints and watchpoints – unlimited software breakpoints.

- Run/stop control of target application including go, halt, step over, step into and step out of.

- Multi-core heterogeneous and homogeneous debug scan-chain support via cJTAG/JTAG/SWD. See here for more details.

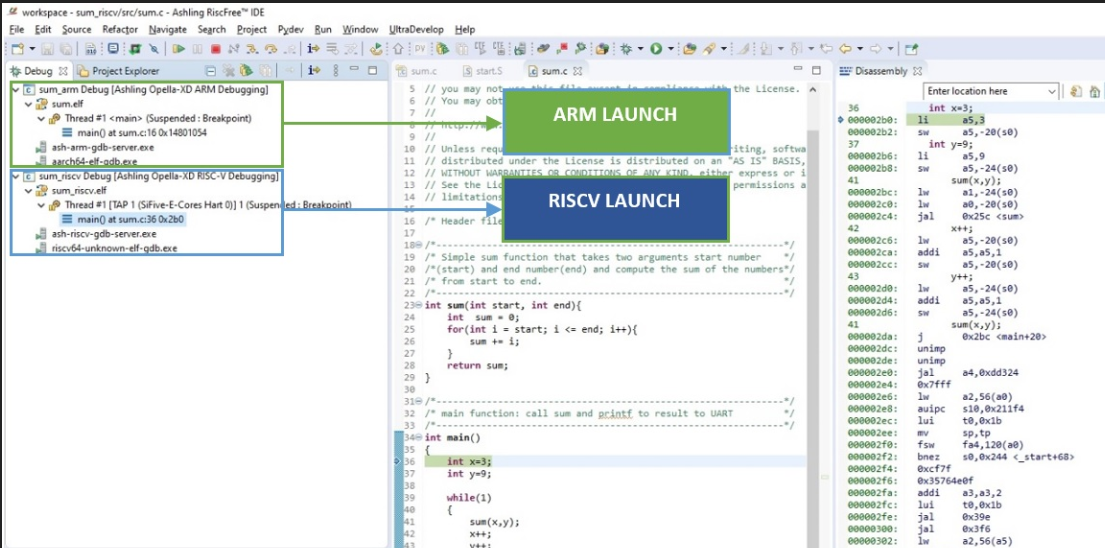

Opella-XD works with RiscFree™, Ashling’s Eclipse-CDT based Integrated Development Environment (IDE) and Debugger. GNU GDB and other third-party debuggers are also supported. Contact Ashling for more details.

Figure 1. RiscFree™ Debug View with Multi-core RISC-V and ARC launches