Ashling’s Tools-as-a-Service™ (TaaS™) model allows development of a comprehensive tool suite tailored and optimised for your specific device.

With the many different configurable processor cores now available (RISC-V, Arm, Synopsys ARC etc), it is now possible to build highly customised devices which are designed specifically to meet your application needs. However, using off-the-shelf “generic” tools will only allow your customers to scratch the surface of your devices capabilities and to allow you and them to get the best out of your device, you need a toolset tailored to take advantage of all the compelling unique features your device offers whether these be Custom Instruction Extensions, Hardware Accelerators, multiple Heterogenous or Homogenous Cores, Crypto Co-processors, Custom Peripherals, Graphical co-processors/GPUs, Hardware Threading etc.

Ashling’s TaaS™ model allows us to jointly develop and rapidly bring this custom tool solution to the market thus giving your device a key, competitive advantage and ensuring your customers can take maximum advantage of everything your device has to offer. TaaS™ offers many benefits including:

- Rapid availability of a customised and optimised toolset for your device including some or all the following: SDK, IDE, Debugger, Compiler Toolchain, Simulators, Hardware Debug and Trace Probes, Reference Boards, OS/RTOS Ports, BSPs, HAL etc.

- Toolset feature priorities and roll-out are defined by you and implemented by us.

- Toolset intellectual property becomes yours (or can be placed in Escrow).

- Toolset can be made available “free-of-charge” to your customers.

- Toolset development, support, maintenance and quality assurance all handled by Ashling.

THE RISC-V EXAMPLE

RISC-V is an open-source ISA (Instruction Set Architecture) which allows users to extend the ISA with their own unique instructions optimised for their application without entering expensive and prohibitive licensing agreements as needed for closed-source cores. ISA extensions can only succeed if the tools solution is able to support these extra instructions both from a Compiler Toolchain and Debugger perspective. Ashling’s TaaS™ model addresses this challenge by providing custom tools supporting the ISA additions which are supported, maintained and regularly updated.

CASE STORIES

Synopsys

Ashling and Synopsys have a multi-year TaaS™ model in place for hardware and software tools development including extension, maintenance and verification of Synopsys’ MetaWare IDE and MDB debugger tools for DesignWare® ARC® processors. One of Ashling’s key differentiators is support and integration of a real-time, trace hardware probe which is key for applications which need non-intrusive debugging and have real-time constraints.

“Synopsys’ collaboration with Ashling on the development of their Ultra-XD real-time trace probe provides developers with integrated tools to accelerate the development and debugging of software for ARC-based embedded systems.” John Koeter, Vice President of Marketing for IP and Prototyping at Synopsys.

In our partnership with Synopsys, we are leveraging our focused engineering expertise and many years of know-how in embedded debug to develop best-in-class debug solutions.

“SoCs targeting embedded applications must meet increasingly stringent cost and power budgets. By adding support for the IEEE’s Compact JTAG standard in their Opella-XD Debug Probe for ARC processor cores, Ashling enables designers to use fewer pins to debug their SoCs containing ARC microprocessors, saving both power and cost.” Mike Thompson, Senior Marketing Manager at Synopsys.

NXP

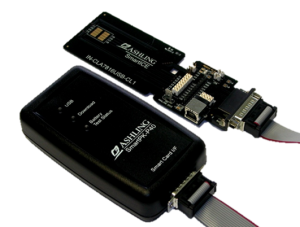

Ashling and NXP have been working closely for over thirty years on the development, supply and support of hardware and software debug solutions for NXP Secure Devices dedicated to the Smart Card, Identification and Secure Transaction markets.

“Ashling, with their extensive experience in embedded software and hardware development, enable NXP customers to rapidly get from design concept to end market with an optimized usage of the resources  and technology we are integrating in our smart card and secure element products.” Gérard Maniez, Director at NXP.

and technology we are integrating in our smart card and secure element products.” Gérard Maniez, Director at NXP.

As part of this agreement, Ashling have also integrated support for their Hardware based SmartICE Debug and Trace probe into the Keil uVision Tools.

“The Ashling SmartICE extends Keil PK51 to a complete solution for target debugging on the SmartMX hardware. SmartICE is fully integrated into the µVision Debugger and gives PK51 users powerful capabilities for program test and verification.” Reinhard Keil, Director of MCU Tools at ARM.

Ashling’s skills and expertise in providing custom tools solutions is unmatched and we have global engineering teams in Ireland and India ready to start working for you now. Please contact us to further discuss your requirements using the form below.

Western Digital

Western Digital and Ashling have a long history of working together on debug tools solutions tailored for Storage Devices including SD Cards (ex-SanDisk) and Hard Disks. More recently, WD have engaged with Ashling to provide customised debug tools solutions based on Ashling’s RiscFree™ for their SweRV RISC-V based cores with a particular emphasis on providing debug support for WD hetereogeneous multi-core SoC designs. RiscFree™ provides a full-development environment for the SweRV RISC-V cores including an IDE, Compiler and Debugger with support for Profiling, Code Coverage, Cacheable Overlay Manager and RTOS awareness (FreeRTOS).

Others (Confidential for now ? )

We are currently working on two separate, confidential projects for top-ten semiconductor companies utilising our RiscFree™ IDE and Debug Probes. Our role involves compiler customisation (custom instructions support and compiler benchmarking, optimization and tuning), real-time trace support (on/off-chip using Arm CoreSight PTM and RISC-V Nexus trace formats), RTOS debug (Zephyr, FreeRTOS and μC/OS) and support for simultaneous, multi-core debugging of SoCs with multiple RISC-V and Arm Cortex-A cores connected via a single CoreSight SWD interface.

It’s challenging and specialist work which requires extensive and close co-operation between both the Ashling and semi-vendor Engineering teams. We are in effect developing the Tools and the SoC in parallel with the goal that first tools will be available with the first SoC simulation allowing their software teams to immediately start integration, debug and validation…all of which of course is key to get a head start in today’s world of diminishing time-to-market.