RiscFree “Best-In-Class” IDE and Unified Debugger for Altera FPGAs.

- Developed by Ashling for Altera.

- Full toolchain including Ashling’s RiscFree for Altera FPGAs IDE, Compiler, Debugger and Trace.

- Works “out-of-the-box” and installed along with the Altera Quartus® FPGA Design Software.

- Provides software development and debug support for Nios V 32-bit and 64-bit (coming soon) soft processors based on the RISC-V ISA.

- Custom instruction support and extensions for the Nios V processor.

- Supports Altera Agilex, Stratix 10, Arria 10 and Cyclone 10 GX FPGA devices.

- Project Manager and Build Manager including Make and CMake support with rapid import, build and debug of Altera Quartus created application frameworks.

- Targeted Nios V GCC compiler toolchain fully integrated into the RiscFree IDE with support for newlib & picolibc run-time libraries using the Nios V Hardware Abstraction Layer (HAL)

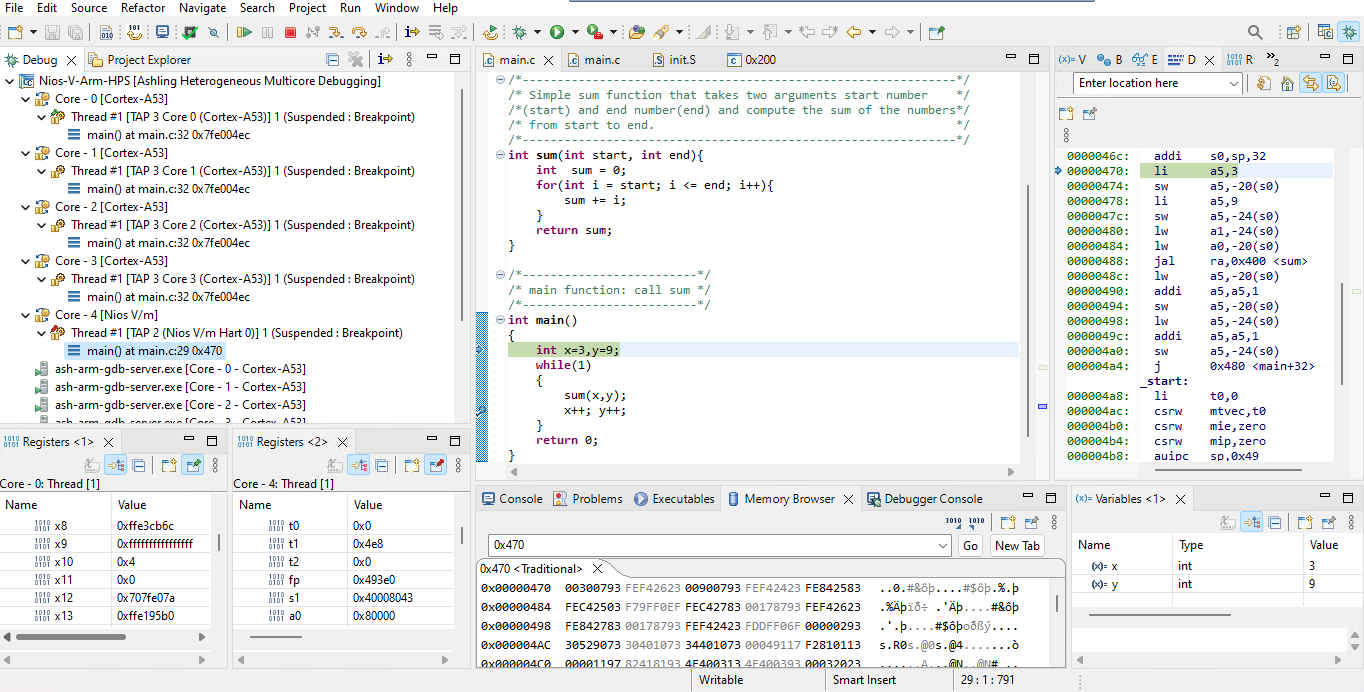

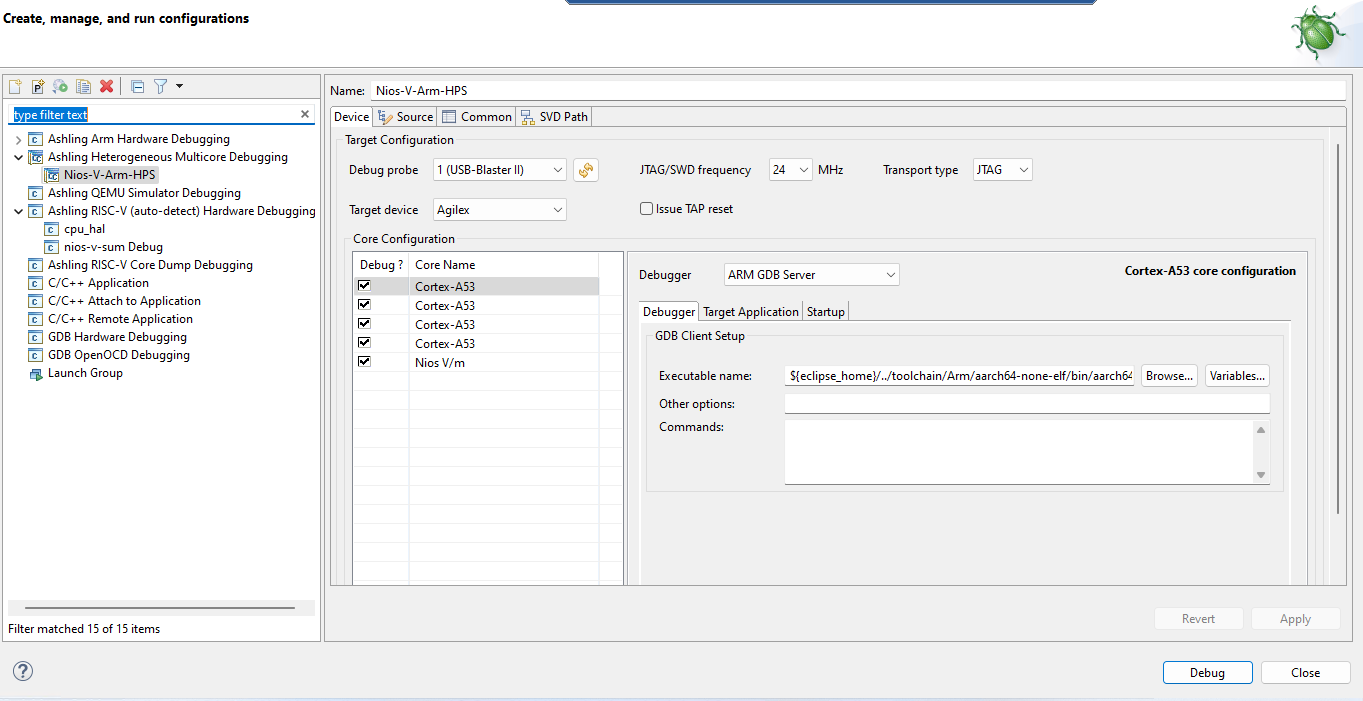

“Different Cores, One Solution.” A single instance of RiscFree supports simultaneous (“Unified”) debugging of any number of heterogeneous or homogeneous Altera FPGA cores including Nios V and Arm.

- Run-time Debug using the Altera FPGA Download Cable II (USB Blaster II).

- Register Visualization for Nios V and Arm cores.

- Heterogeneous and homogeneous simultaneous multi-core debug support for Nios V and Arm cores.

- Zephyr, FreeRTOS and μC/OS RTOS debug awareness.

- Full target Linux OS (multi-core/multi-hart) kernel, device driver and application debug support.

- Real-time Trace (on-chip and off-chip) support for both Nios V and Arm cores. Off-chip trace requires the Ashling Vitra trace probe available from Ashling.

- Altera’s Simics Nios V simulator support.

*Altera, the Altera logo, and other Altera marks are trademarks of Altera Corporation or its subsidiaries.