Opella-LD Debug Probe

Overview

Ashling’s Opella-LD is Ashling’s low-cost Debug Probe for embedded development with support for multiple target architectures including Arm, RISC-V and Synopsys ARC powered systems.

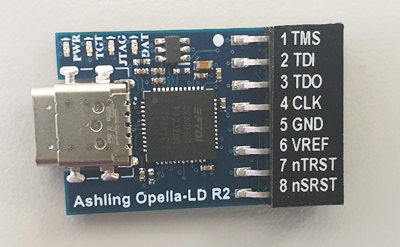

Figure 1. The Ashling Opella-LD Debug Probe

Opella-LD software debug support is provided via the open-source OpenOCD standard and provides fast code download to the target system with control and interrogation support for all core and system resources including registers and memory. OpenOCD allows debugging via GNU GDB and Ashling’s RiscFree™, Eclipse-CDT based Integrated Development Environment (IDE) and Debugger. Note: the Synopsys ARC Core MetaWare Development Toolkit (MWDT) including the ARC MDB or MIDE debuggers are not supported by Opella-LD. Please use Opella-XD.

Opella-LD features

- Low-cost, compact form-factor.

- Works with Arm, RISC-V and Synopsys ARC powered systems.

- Works with Windows and Linux hosts.

- On-board USB Type-C host PC interface.

- Supports JTAG, cJTAG and CoreSight SWD debug interfaces with up to 30MHz data clock rates.

- Four LEDs to indicate Power, Target Present, JTAG or SWD mode and Data Transfer Activity.

- Supports and automatically adapts to target voltages between 0.9v and 5.0v.

- Supports JTAG TAP Reset (TRST) and System Reset (SRST).

- Dedicated site with latest user documentation, drivers and OpenOCD configuration files for all target architectures.

Opella-LD is provided with “flying-leads” allowing easy connection to your target. Dedicated adapters are also available for standard target footprints such as MIPI/Arm Coresight 10-way.