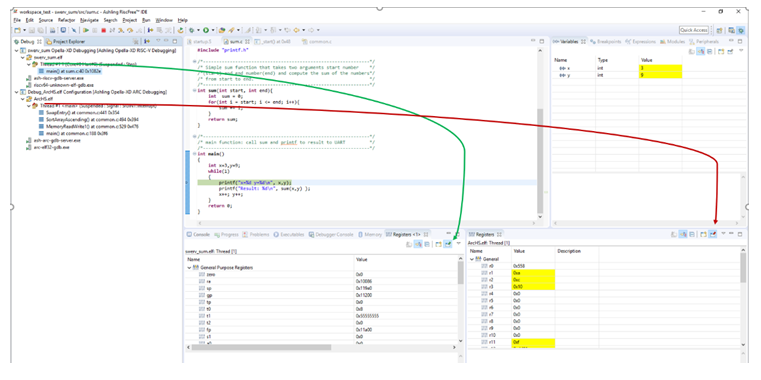

Today, System-on-Chip (SoC) design is becoming more complex as chip designers pack more and more features on to a single device to meet market demands including features, performance and power-consumption requirements.

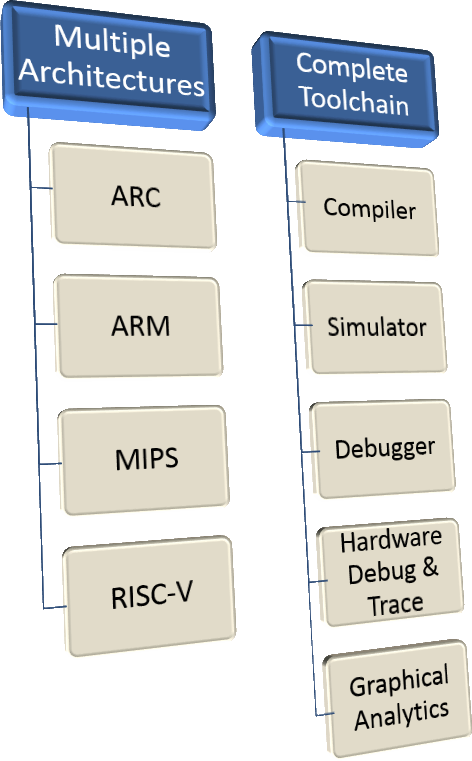

As process technology improvements reach their limits (the end of Moore’s law), designers are continuing the move to multi-core designs and are integrating different processor architectures (i.e. heterogeneous cores) such as Arm, RISC-V, ARC (Synopsys) and MIPS onto a single SoC.