Compiler, IDE and Debugger Toolchain Services

Compiler Toolchain Services

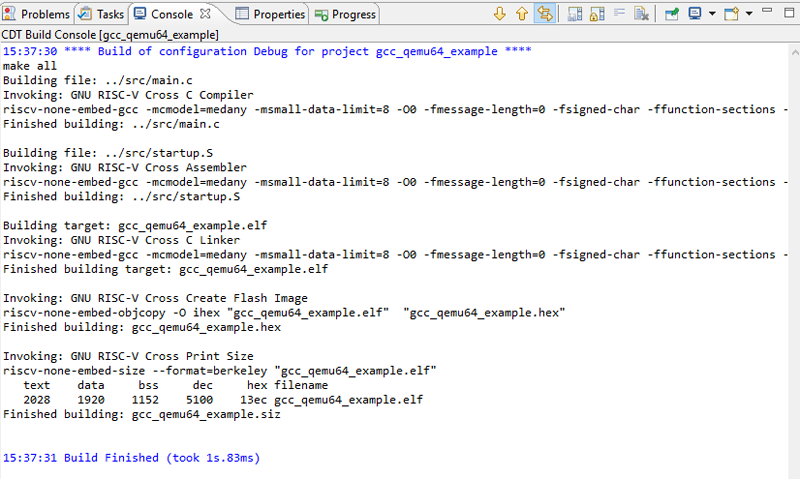

Ashling provide customised compiler toolchains tailored for your needs and requirements based on either the open-source GNU GCC or LLVM distributions along with the QEMU ISA simulator and debug support. For larger projects, we sometimes work together with our long-term partner Embecosm, an open-source software toolchain company.

Figure 1. Building using the GNU GCC Compiler

Figure 1. Building using the GNU GCC Compiler

Our expertise includes:

- GNU GCC and LLVM toolchains including compiler, linker, assembler, binutils, run-time libraries and debuggers (GDB, OpenOCD, Eclipse CDT etc.).

- Arm, MIPS, RISC-V and Synopsys ARC architecture support.

- Improving optimization (i.e. code generation in terms of speed and code-size) of the toolchain at both a compiler and linker level.

- Support for custom instructions (ISA extensions) including support in the compiler toolchain, QEMU ISA simulator and debuggers. See Ashling white paper on adding custom RISC-V instructions to QEMU here.

- New run-time libraries and optimization of existing libraries.

- Ensuring the toolchain is kept up to date with all other community updates (e.g. quarterly updates/releases).

- Compliance, certification and qualification of the toolchain e.g. to ISO26262 and IEC61508 standards.

- Testing, verification and bug-fixing of the toolchain on both software simulators and real target hardware.

Common Vulnerability & Exposures

Ashling offer Common Vulnerability & Exposures (CVEs) identification and remediation support. A CVE is a publicly disclosed security vulnerability that may exist in an open-source toolchain (e.g. the compiler) or the run-time target libraries. CVEs in run-time libraries are particularly problematic as they may end up also being present i.e. “linked-in” to the end-user’s target application. If required, we will take all reasonable steps to ensure CVEs are remediated (i.e. “patched and removed”) before releasing toolchain versions thus allowing you to provide a high-level of security to both your internally developed applications and those of your toolchain end-users. For more details see here.

IDE and Debugger Services

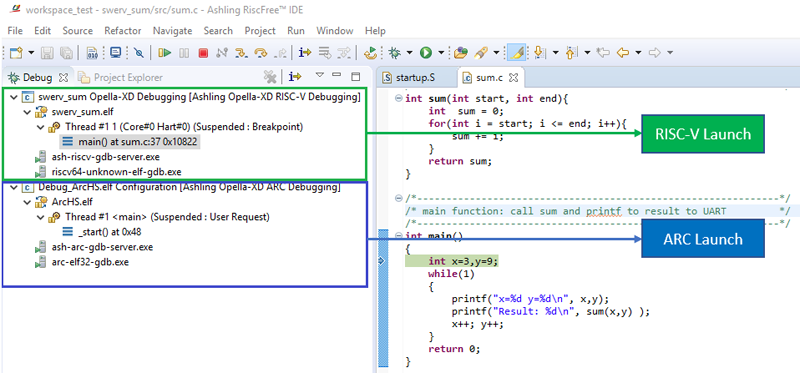

RiscFree™ is Ashling’s Eclipse-CDT based Integrated Development Environment (IDE) and Debugger which can be customised and tailored for your needs and requirements.

Figure 2. RiscFree™ Debug View with Multi-core RISC-V and ARC launches

Figure 2. RiscFree™ Debug View with Multi-core RISC-V and ARC launches

RiscFree™ features include:

- IDE based on Eclipse with full source and project creation, editing, build and debug support.

- Integrated GCC and/or LLVM compiler toolchains.

- Please see here for more details on RiscFree™