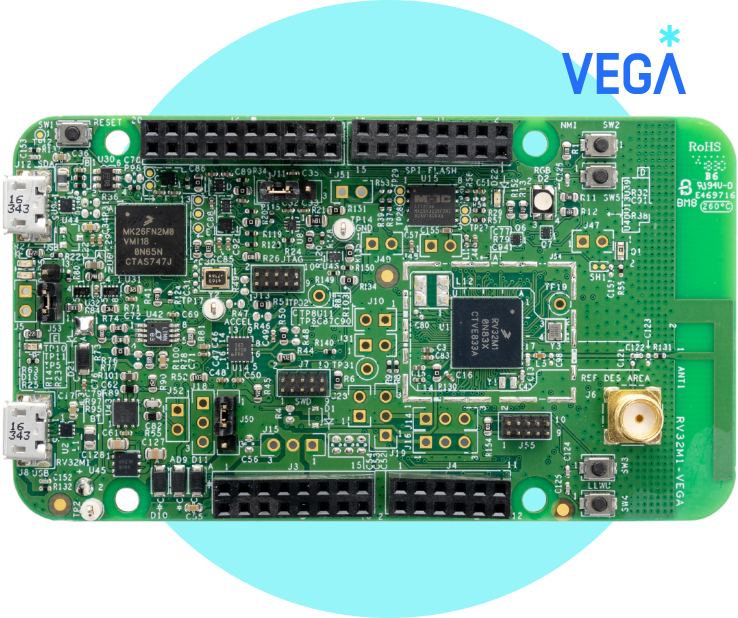

Ashling RiscFree™ C/C++ Development Suite for PULP RISC‑V Devices

Ashling provides a comprehensive tools solution for PULP RISC-V based cores, including C/C++ cross-compiler support for any RISC-V ISA with custom extensions. This includes Ashling’s RiscFree™ Eclipse-based Integrated Development Environment (IDE) for RISC-V, which provides a complete, seamless environment for RISC‑V software development.

|

|

|

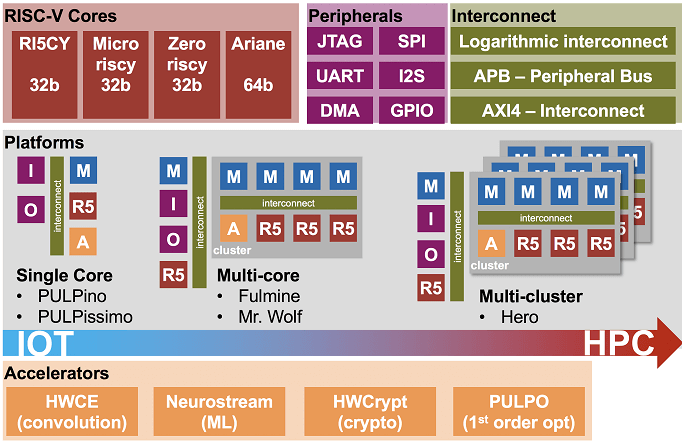

PULP Features

- Efficient implementations of RISC-V cores. These include:

- 32 bit 4-stage core RI5CY

- 32 bit 2-stage Zero-riscy and Micro-riscy

- 64 bit 6-stage Ariane

- Complete systems based on:

- single-core micro-controllers (PULPissimo, PULPino)

- multi-core IoT Processors (OpenPULP)

- multi-cluster heterogeneous accelerators (Hero)

- Open-source SolderPad license

- a perpetual, worldwide, non-exclusive, no-charge, royalty-free, irrevocable license

- Rich set of peripherals

- I2C, SPI, HyperRAM, GPIO

RiscFree™ Features

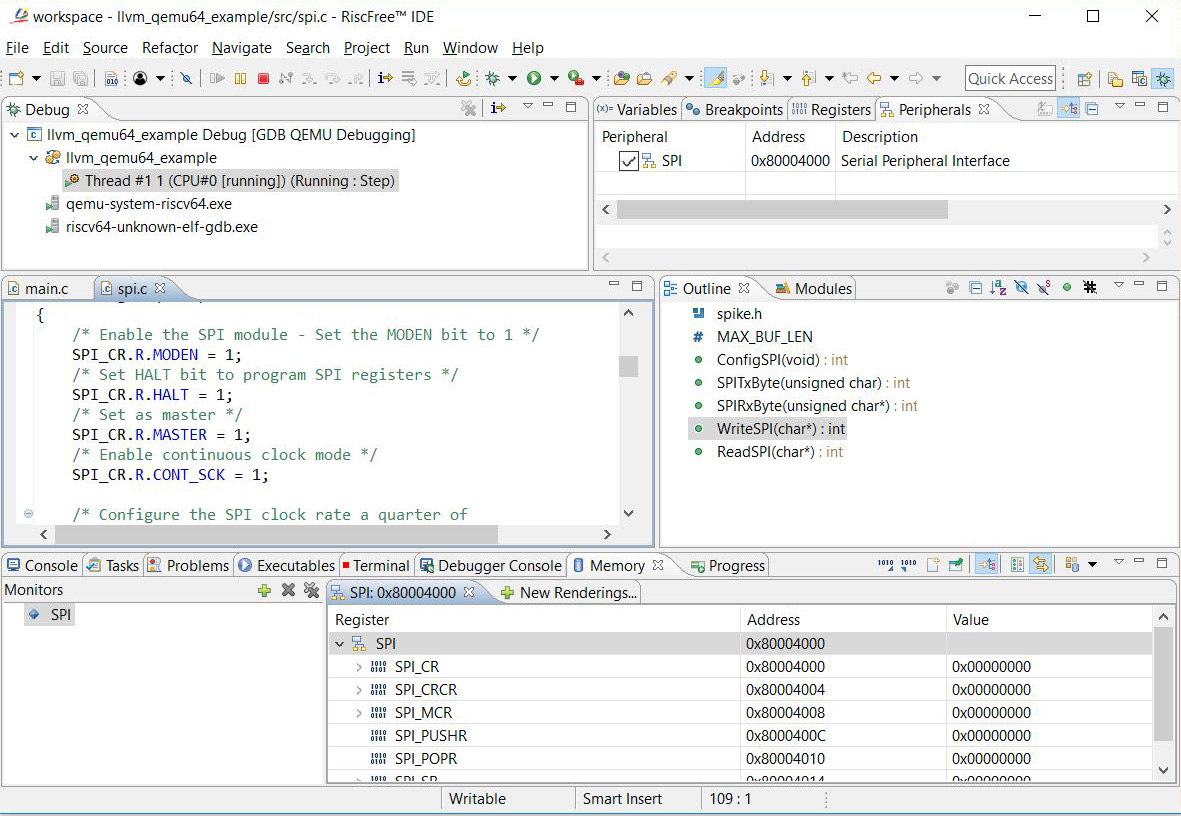

- IDE based on Eclipse with full source and project creation, editing, build and integrated debug support

- Includes automatic source-code formatting, syntax coloring and function folding

- Includes a single-shot installer that installs and automatically configures all the component tools to work “out-of-the-box”.

- Project wizards and examples allowing you to quickly create projects from scratch or use the pre-built examples

- Full compiler toolchain including an optimizing C/C++ compiler, assembler and linker including start-up code and run-time libraries. Compiler toolchains support optional user specific customisations, see our compiler and tools services for more details

- Hardware Debug (Opella-XD) and Trace probe options fully integrated into the Debugger allowing debug and easy setup, capture and display of Trace and Profiling data

- Multi-core debug support

- On-chip trace and debug analytics support

- ROM or RAM based debugging support (e.g. hardware breakpoints for flash-based support)

- Includes QEMU ISA simulator for 32 and 64-bit RISC-V cores

- High-level RISC-V Register Viewer (XML database driven)

- Integrated RTOS debug support

- Integrated Serial Terminal

- Script language for automating debugging sessions

Tools Customization

Ashling’s Tools-as-a-Service (TaaS™) offers many benefits to PULP users including:

- Rapid availability of a customized and optimized toolset for your device including some or all of the following: IDE, Debugger, Compiler Toolchain, Simulators, Hardware Debug and Trace Probes, Operating Systems, BSPs etc.

- Toolset feature priorities and roll-out defined by you and implemented by us

- Toolset intellectual property becomes yours (or can be placed in Escrow)

- Toolset can be made available “free-of-charge” to your customers

- Toolset development, support, maintenance and quality assurance all handled by Ashling

Opella-XD for PULP RISC-V JTAG Probe

Ashling’s Opella-XD is a high-speed JTAG debug probe for embedded development on RISC-V cores. Opella-XD for RISC-V is the latest in a number of high speed debug probes supporting MCU, SoC, and Soft (FPGA) based designs and highlighting 35+ years of experience developing and building embedded development tools.

Features of Opella-XD for RISC-V:

- Fast, trouble-free “plug-and-play” installation using USB 2.0 High-Speed Interface (480Mb/s)

- Up to 3MB/s download speeds particularly suitable for large, complex projects

- Fully powered by USB interface; no external power-supply needed

- Fine-grained adjustment of JTAG clock frequency from 1KHz to 100MHz.

- Multi-core support with full JTAG scan-chain configurability

- Detects and automatically configures for the appropriate target voltage from 0.9V to 3.6V

- Fast in-target Flash and FPGA Programming

- Support for all on-chip hardware breakpoints; unlimited number of software breakpoints

- Configurable Target-Reset and Test-Port-Reset, under full user control

- Built-in diagnostics instantly show status of Target, Debug Probe and USB link

RiscFree™ Evaluation Download

Please fill the form below to request a Password to download the RiscFree™ for RISC-V evaluation.

* RiscFree™ tools are free to use for non-commercial applications or evaluation. Please refer to our licensing terms and conditions below.